zachj00

Jr. Member

Offline Offline

Activity: 120

Merit: 2

|

|

January 16, 2019, 09:15:44 PM |

|

I have the version 1.1, 8.6 THs model. I only run it at 550 MHz though so I just say its 7.9 THs

Its says my Kernel is 2016 and my file system is 2017.

|

|

|

|

|

|

|

|

|

|

"Bitcoin: the cutting edge of begging technology." -- Giraffe.BTC

|

|

|

Advertised sites are not endorsed by the Bitcoin Forum. They may be unsafe, untrustworthy, or illegal in your jurisdiction.

|

Artemis3

Legendary

Offline Offline

Activity: 2016

Merit: 1563

CLEAN non GPL infringing code made in Rust lang

|

|

January 17, 2019, 12:58:14 PM |

|

I have the version 1.1, 8.6 THs model. I only run it at 550 MHz though so I just say its 7.9 THs

Its says my Kernel is 2016 and my file system is 2017.

Are you sure you downloaded the files correctly? Please verify your downloaded files integrity: - Antminer-R4-all-201704280718-autofreq-user-Update2UBI-NF.tar.gz

File size & date: 63666471 jul 31 01:59

md5sum: 7f541a58a4ee559105894c94ff301108

sha256sum: 4746c338403446c14dd2e9e299d7f31ad325bf434fb0327bb29d2e48eed4aa6c - Antminer-R4-xilinx-201811121649-autofreq-user-UBI-NF.tar.gz

File size & date: 19827412 nov 19 03:22

md5sum: 94d6f3cee5bcc2b097e85046cbcbb7ad

sha256sum: 81fc732125c586f44726e7f1f5eefcdf920d22d8d504f17d7ce0723020bba1b8

And make sure you use firefox or chromium based browsers. If your file system is from 2017, it might mean you already have the UBI firmware. Did you not remember ever upgrading the firmware? In that case, all you need is the 2018 update. Just in case copy and paste your file system version (maybe the month matters). |

█████████████████████████

██████████████████████████

██████████████████████████

███████████████████████████ | BRAIINS OS+| | AUTOTUNING

MINING FIRMWARE| | Increase hashrate on your Bitcoin ASICs,

improve efficiency as much as 25%, and

get 0% pool fees on Braiins Pool | |

|

|

|

zachj00

Jr. Member

Offline Offline

Activity: 120

Merit: 2

|

|

January 18, 2019, 09:01:01 PM |

|

I upgraded to the 2017 firmware and then tried the 2018 firmware after and I get an instant error message saying its the wrong file type or something along the lines of that. I know the R4s can be a bit fragile and every time i try to upgrade my board temps go crazy and it scares me a bit. It takes my R4 a few minutes before the fan really starts spinning every restart and the chip readings will hit the 90s. I think ill just keep the adjustable MHz version for now. I like to keep it on the lowest setting to keep board temps to a minimum.

|

|

|

|

|

Artemis3

Legendary

Offline Offline

Activity: 2016

Merit: 1563

CLEAN non GPL infringing code made in Rust lang

|

|

January 18, 2019, 09:21:53 PM |

|

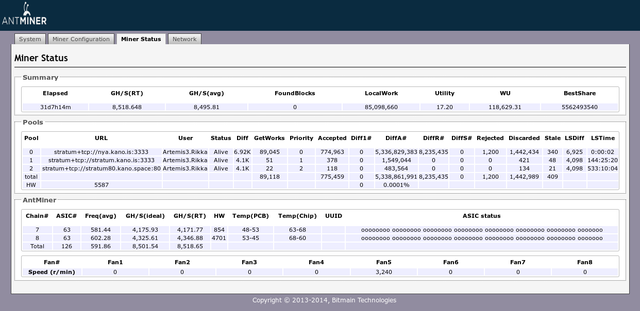

I upgraded to the 2017 firmware and then tried the 2018 firmware after and I get an instant error message saying its the wrong file type or something along the lines of that. I know the R4s can be a bit fragile and every time i try to upgrade my board temps go crazy and it scares me a bit. It takes my R4 a few minutes before the fan really starts spinning every restart and the chip readings will hit the 90s. I think ill just keep the adjustable MHz version for now. I like to keep it on the lowest setting to keep board temps to a minimum. If you are worried why don't you let the fan blow at 100%? That's how mine has always been running. With the older firmware i would sometimes see crazy temperatures (max i saw was 120) but with the newer firmware 74 is the max i have seen so far, and instead of two readings you get 4, it seems far more accurate than before. Here look:  I upgraded that R4 from 2016 firmware to 2017 and then to 2018 without any errors. Do check the file integrity of your 2018 firmware download. |

█████████████████████████

██████████████████████████

██████████████████████████

███████████████████████████ | BRAIINS OS+| | AUTOTUNING

MINING FIRMWARE| | Increase hashrate on your Bitcoin ASICs,

improve efficiency as much as 25%, and

get 0% pool fees on Braiins Pool | |

|

|

|

sarcheer

Copper Member

Full Member

Offline Offline

Activity: 330

Merit: 103

|

|

January 18, 2019, 09:31:01 PM |

|

I upgraded to the 2017 firmware and then tried the 2018 firmware after and I get an instant error message saying its the wrong file type or something along the lines of that. I know the R4s can be a bit fragile and every time i try to upgrade my board temps go crazy and it scares me a bit. It takes my R4 a few minutes before the fan really starts spinning every restart and the chip readings will hit the 90s. I think ill just keep the adjustable MHz version for now. I like to keep it on the lowest setting to keep board temps to a minimum.

Is it possible you're one of the few with an incompatible control board? Can you post the start up sequence from the kernel log? Curious if you have neither 512 or 1024 mb like mentioned in the FW title. Also, check and see if your control board says XILINX on it. If not, the AB FW is incompatible with your board. |

Miners:

Avalon 1041, Whatsminer M10, Antminer T15 x 2, DragonMint T1 x 3, Innosilicon T2T, R4 x 2

|

|

|

zachj00

Jr. Member

Offline Offline

Activity: 120

Merit: 2

|

|

January 18, 2019, 09:54:27 PM

Last edit: January 18, 2019, 10:34:40 PM by zachj00 |

|

Heres the first part of the kernal log. Booting Linux on physical CPU 0x0

Initializing cgroup subsys cpuset

Linux version 3.10.31-ltsi-00003-gcf03eb9 (lzq@armdev01) (gcc version 4.7.3 20121106 (prerelease) (crosstool-NG linaro-1.13.1-4.7-2012.11-20121123 - Linaro GCC 2012.11) ) #81 SMP Mon Apr 25 11:20:36 CST 2016

CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=10c5387d

CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

Machine: Altera SOCFPGA, model: Altera SOCFPGA Cyclone V

Memory policy: ECC disabled, Data cache writealloc

On node 0 totalpages: 258048

free_area_init_node: node 0, pgdat 806e5cc0, node_mem_map 8072a000

Normal zone: 2016 pages used for memmap

Normal zone: 0 pages reserved

Normal zone: 258048 pages, LIFO batch:31

PERCPU: Embedded 8 pages/cpu @80f17000 s11200 r8192 d13376 u32768

pcpu-alloc: s11200 r8192 d13376 u32768 alloc=8*4096

pcpu-alloc: [0] 0 [0] 1

Built 1 zonelists in Zone order, mobility grouping on. Total pages: 256032

Kernel command line: mem=1008M console=ttyS0,115200 root=/dev/mtdblock3 rw rootfstype=jffs2

PID hash table entries: 4096 (order: 2, 16384 bytes)

Dentry cache hash table entries: 131072 (order: 7, 524288 bytes)

Inode-cache hash table entries: 65536 (order: 6, 262144 bytes)

Memory: 1008MB = 1008MB total

Memory: 1015844k/1015844k available, 16348k reserved, 0K highmem

Virtual kernel memory layout:

vector : 0xffff0000 - 0xffff1000 ( 4 kB)

fixmap : 0xfff00000 - 0xfffe0000 ( 896 kB)

vmalloc : 0xbf800000 - 0xff000000 (1016 MB)

lowmem : 0x80000000 - 0xbf000000 (1008 MB)

modules : 0x7f000000 - 0x80000000 ( 16 MB)

.text : 0x80008000 - 0x8065a930 (6475 kB)

.init : 0x8065b000 - 0x806adbc0 ( 331 kB)

.data : 0x806ae000 - 0x806e9990 ( 239 kB)

.bss : 0x806e9990 - 0x80729384 ( 255 kB)

SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1

Hierarchical RCU implementation.

NR_IRQS:16 nr_irqs:16 16

sched_clock: 32 bits at 100MHz, resolution 10ns, wraps every 42949ms

Console: colour dummy device 80x30

Calibrating delay loop... 1196.85 BogoMIPS (lpj=5984256)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 512

CPU: Testing write buffer coherency: ok

ftrace: allocating 17687 entries in 52 pages

CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

Setting up static identity map for 0x804ab220 - 0x804ab278

CPU1: failed to come online

Brought up 1 CPUs

SMP: Total of 1 processors activated (1196.85 BogoMIPS).

CPU: All CPU(s) started in SVC mode.

devtmpfs: initialized

NET: Registered protocol family 16

fpga bridge driver

DMA: preallocated 256 KiB pool for atomic coherent allocations

L310 cache controller enabled

l2x0: 8 ways, CACHE_ID 0x410030c9, AUX_CTRL 0x32460000, Cache size: 524288 B

syscon fffef000.l2-cache: regmap [mem 0xfffef000-0xfffeffff] registered

syscon ffd05000.rstmgr: regmap [mem 0xffd05000-0xffd05fff] registered

syscon ffc25000.sdrctl: regmap [mem 0xffc25000-0xffc25fff] registered

syscon ff800000.l3regs: regmap [mem 0xff800000-0xff800fff] registered

syscon ffd08000.sysmgr: regmap [mem 0xffd08000-0xffd0bfff] registered

hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers.

hw-breakpoint: maximum watchpoint size is 4 bytes.

altera_hps2fpga_bridge fpgabridge.2: fpga bridge [hps2fpga] registered as device hps2fpga

altera_hps2fpga_bridge fpgabridge.2: init-val not specified

altera_hps2fpga_bridge fpgabridge.3: fpga bridge [lshps2fpga] registered as device lwhps2fpga

altera_hps2fpga_bridge fpgabridge.3: init-val not specified

altera_hps2fpga_bridge fpgabridge.4: fpga bridge [fpga2hps] registered as device fpga2hps

altera_hps2fpga_bridge fpgabridge.4: init-val not specified

bio: create slab <bio-0> at 0

FPGA Mangager framework driver

SCSI subsystem initialized

usbcore: registered new interface driver usbfs

usbcore: registered new interface driver hub

usbcore: registered new device driver usb

pps_core: LinuxPPS API ver. 1 registered

pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

PTP clock support registered

Switching to clocksource timer0

NET: Registered protocol family 2

TCP established hash table entries: 8192 (order: 4, 65536 bytes)

TCP bind hash table entries: 8192 (order: 4, 65536 bytes)

TCP: Hash tables configured (established 8192 bind 8192)

TCP: reno registered

UDP hash table entries: 512 (order: 2, 16384 bytes)

UDP-Lite hash table entries: 512 (order: 2, 16384 bytes)

NET: Registered protocol family 1

RPC: Registered named UNIX socket transport module.

RPC: Registered udp transport module.

RPC: Registered tcp transport module.

RPC: Registered tcp NFSv4.1 backchannel transport module.

hw perfevents: enabled with ARMv7 Cortex-A9 PMU driver, 7 counters available

arm-pmu arm-pmu: PMU:CTI successfully enabled for 1 cores

NFS: Registering the id_resolver key type

Key type id_resolver registered

Key type id_legacy registered

NTFS driver 2.1.30 [Flags: R/W].

jffs2: version 2.2. (NAND) © 2001-2006 Red Hat, Inc.

msgmni has been set to 1984

io scheduler noop registered (default)

Serial: 8250/16550 driver, 2 ports, IRQ sharing disabled

ffc02000.serial0: ttyS0 at MMIO 0xffc02000 (irq = 194) is a 16550A

console [ttyS0] enabled

altera_fpga_manager ff706000.fpgamgr: fpga manager [Altera FPGA Manager] registered as minor 0

brd: module loaded

denali-nand-dt ff900000.nand: Dump timing register values:acc_clks: 4, re_2_we: 20, re_2_re: 20

we_2_re: 12, addr_2_data: 14, rdwr_en_lo_cnt: 2

rdwr_en_hi_cnt: 2, cs_setup_cnt: 2

ONFI param page 0 valid

ONFI flash detected

NAND device: Manufacturer ID: 0x2c, Chip ID: 0xda (Micron MT29F2G08ABAEAWP), 256MiB, page size: 2048, OOB size: 64

Bad block table found at page 131008, version 0x01

Bad block table found at page 130944, version 0x01

5 ofpart partitions found on MTD device denali-nand

Creating 5 MTD partitions on "denali-nand":

0x000000000000-0x000001000000 : "NAND Flash Boot Area 16MB"

0x000001000000-0x000002000000 : "NAND Flash Boot Area backup1 16MB"

0x000002000000-0x000003000000 : "NAND Flash Boot Area backup2 16MB"

0x000003000000-0x00000b000000 : "NAND Flash jffs2 Root Filesystem 128MB"

0x00000b000000-0x000010000000 : "NAND Flash jffs2 Root Filesystem 80MB"

dw_spi_mmio fff00000.spi: master is unqueued, this is deprecated

CAN device driver interface

c_can_platform ffc00000.d_can: invalid resource

c_can_platform ffc00000.d_can: control memory is not used for raminit

c_can_platform ffc00000.d_can: c_can_platform device registered (regs=bf8dc000, irq=163)

stmmac_hw_init: 1000M

stmmac - user ID: 0x10, Synopsys ID: 0x37

Ring mode enabled

DMA HW capability register supported

Enhanced/Alternate descriptors

Enabled extended descriptors

RX Checksum Offload Engine supported (type 2)

TX Checksum insertion supported

Enable RX Mitigation via HW Watchdog Timer

libphy: stmmac: probed

eth0: PHY ID 0007c0f1 at 0 IRQ POLL (stmmac-0:00) active

usbcore: registered new interface driver usb-storage

mousedev: PS/2 mouse device common for all mice

i2c /dev entries driver

Synopsys Designware Multimedia Card Interface Driver

dwmmc_socfpga ff704000.dwmmc0: couldn't determine pwr-en, assuming pwr-en = 0

dwmmc_socfpga ff704000.dwmmc0: Using internal DMA controller.

dwmmc_socfpga ff704000.dwmmc0: Version ID is 240a

dwmmc_socfpga ff704000.dwmmc0: DW MMC controller at irq 171, 32 bit host data width, 1024 deep fifo

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 400000Hz, actual 396825HZ div = 63)

dwmmc_socfpga ff704000.dwmmc0: 1 slots initialized

ledtrig-cpu: registered to indicate activity on CPUs

usbcore: registered new interface driver usbhid

usbhid: USB HID core driver

oprofile: using arm/armv7-ca9

TCP: cubic registered

NET: Registered protocol family 10

sit: IPv6 over IPv4 tunneling driver

NET: Registered protocol family 17

NET: Registered protocol family 15

can: controller area network core (rev 20120528 abi 9)

NET: Registered protocol family 29

can: raw protocol (rev 20120528)

can: broadcast manager protocol (rev 20120528 t)

can: netlink gateway (rev 20130117) max_hops=1

8021q: 802.1Q VLAN Support v1.8

Key type dns_resolver registered

VFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4

ThumbEE CPU extension supported.

Registering SWP/SWPB emulation handler

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 300000Hz, actual 297619HZ div = 84)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 200000Hz, actual 200000HZ div = 125)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 100000Hz, actual 100000HZ div = 250)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 400000Hz, actual 396825HZ div = 63)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 300000Hz, actual 297619HZ div = 84)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 200000Hz, actual 200000HZ div = 125)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 100000Hz, actual 100000HZ div = 250)

jffs2: Empty flash at 0x01379264 ends at 0x01379800

jffs2: jffs2_scan_inode_node(): CRC failed on node at 0x026f5ff4: Read 0xffffffff, calculated 0x1490a44b

jffs2: Empty flash at 0x026f604c ends at 0x026f6800

jffs2: jffs2_scan_inode_node(): CRC failed on node at 0x053257d0: Read 0xffffffff, calculated 0x89a57f3a

jffs2: Empty flash at 0x05325828 ends at 0x05326000

jffs2: Empty flash at 0x06d4a440 ends at 0x06d4a800

jffs2: Empty flash at 0x071cc00c ends at 0x071cc800

jffs2: jffs2_scan_inode_node(): CRC failed on node at 0x072d0fc8: Read 0xffffffff, calculated 0x05c6c1f6

VFS: Mounted root (jffs2 filesystem) on device 31:3.

devtmpfs: mounted

Freeing unused kernel memory: 328K (8065b000 - 806ad000)

eth0: device MAC address 6e:1f:aa:4f:59:2e

init phy ok

PHY DMA init OK

eth0: device MAC address 00:87:9f:01:9a:3e

init phy ok

PHY DMA init OK

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

libphy: stmmac-0:00 - Link is Up - 100/Full

IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

libphy: stmmac-0:00 - Link is Down

In axi fpga driver!

Original value in RESET_MANAGER_BASE_ADDR + BRGMODRST_ADDR is 0x0

request_mem_region OK!

AXI fpga dev virtual address is 0xbf942000

*base_vir_addr = 0xc50f

In fpga mem driver!

request_mem_region OK!

fpga mem virtual address is 0xc0000000

libphy: stmmac-0:00 - Link is Up - 100/Full

eth0: device MAC address 00:87:9f:01:9a:3e

init phy ok

PHY DMA init OK

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

eth0: device MAC address 00:87:9f:01:9a:3e

init phy ok

PHY DMA init OK

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

libphy: stmmac-0:00 - Link is Up - 100/Full

IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

libphy: stmmac-0:00 - Link is Down

libphy: stmmac-0:00 - Link is Up - 100/Full

This is C5 board.

DETECT HW version=0000c50f

Miner Type = R4

AsicType = 1387

real AsicNum = 63

get PLUG ON=0x00000005

Find hashboard on Chain[0]

Find hashboard on Chain[2]

set_reset_allhashboard = 0x0000ffff

Check chain[0] PIC fw version=0x03

Check chain[2] PIC fw version=0x03

chain[0] has no freq in PIC! Will use default freq=550 and jump over...

Check chain[0] PIC fw version=0x03

chain[2] has no freq in PIC! Will use default freq=550 and jump over...

Check chain[2] PIC fw version=0x03

get PIC voltage=91 on chain[0], value=890

get PIC voltage=91 on chain[2], value=890

set_reset_allhashboard = 0x00000000

chain[0] temp offset record: 3,-71,4,-88,0,0,0,0

chain[2] temp offset record: 3,-81,4,-108,0,0,0,0

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

CRC error counter=0

set command mode to VIL

--- check asic number

set_baud=0

The min freq=700

set real timeout 52, need sleep=379392

After TEST CRC error counter=0

search freq for 1 times, completed chain = 2, total chain num = 2

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

restart Miner chance num=2

waiting for receive_func to exit!

waiting for pic heart to exit!

Start bmminer ...

This is C5 board.

Miner Type = R4

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x0000ffff

Check chain[0] PIC fw version=0x03

Check chain[2] PIC fw version=0x03

Chain[J1] orignal chain_voltage_pic=91 value=890

Chain[J3] orignal chain_voltage_pic=91 value=890

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

Chain[J1] has 63 asic

Chain[J3] has 63 asic

Chain[J1] has no freq in PIC, set default freq=550M

Chain[J1] has no core num in PIC

Chain[J3] has no freq in PIC, set default freq=550M

Chain[J3] has no core num in PIC

read PIC voltage=940 on chain[0]

Chain:0 chipnum=63

Chain[J1] voltage added=0.0V

Chain:0 temp offset=0

Chain:0 base freq=550

Asic[ 0]:550

Asic[ 1]:550 Asic[ 2]:550 Asic[ 3]:550 Asic[ 4]:550 Asic[ 5]:550 Asic[ 6]:550 Asic[ 7]:550 Asic[ 8]:550

Asic[ 9]:550 Asic[10]:550 Asic[11]:550 Asic[12]:550 Asic[13]:550 Asic[14]:550 Asic[15]:550 Asic[16]:550

Asic[17]:550 Asic[18]:550 Asic[19]:550 Asic[20]:550 Asic[21]:550 Asic[22]:550 Asic[23]:550 Asic[24]:550

Asic[25]:550 Asic[26]:550 Asic[27]:550 Asic[28]:550 Asic[29]:550 Asic[30]:550 Asic[31]:550 Asic[32]:550

Asic[33]:550 Asic[34]:550 Asic[35]:550 Asic[36]:550 Asic[37]:550 Asic[38]:550 Asic[39]:550 Asic[40]:550

Asic[41]:550 Asic[42]:550 Asic[43]:550 Asic[44]:550 Asic[45]:550 Asic[46]:550 Asic[47]:550 Asic[48]:550

Asic[49]:550 Asic[50]:550 Asic[51]:550 Asic[52]:550 Asic[53]:550 Asic[54]:550 Asic[55]:550 Asic[56]:550

Asic[57]:550 Asic[58]:550 Asic[59]:550 Asic[60]:550 Asic[61]:550 Asic[62]:550

Chain:0 max freq=550

Chain:0 min freq=550

|

|

|

|

|

NotFuzzyWarm

Legendary

Offline Offline

Activity: 3612

Merit: 2494

Evil beware: We have waffles!

|

|

January 18, 2019, 10:01:12 PM |

|

@ZachJ00 DUDE! Please use the CODE tag before posting another wall of text.... It looks like #Your wall then becomes a much more readable Booting Linux on physical CPU 0x0

Initializing cgroup subsys cpuset

Linux version 3.10.31-ltsi-00003-gcf03eb9 (lzq@armdev01) (gcc version 4.7.3 20121106 (prerelease) (crosstool-NG linaro-1.13.1-4.7-2012.11-20121123 - Linaro GCC 2012.11) ) #81 SMP Mon Apr 25 11:20:36 CST 2016

CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=10c5387d

CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

Machine: Altera SOCFPGA, model: Altera SOCFPGA Cyclone V

Memory policy: ECC disabled, Data cache writealloc

On node 0 totalpages: 258048

free_area_init_node: node 0, pgdat 806e5cc0, node_mem_map 8072a000

Normal zone: 2016 pages used for memmap

Normal zone: 0 pages reserved

Normal zone: 258048 pages, LIFO batch:31

PERCPU: Embedded 8 pages/cpu @80f17000 s11200 r8192 d13376 u32768

pcpu-alloc: s11200 r8192 d13376 u32768 alloc=8*4096

pcpu-alloc:

0

1

Built 1 zonelists in Zone order, mobility grouping on. Total pages: 256032

Kernel command line: mem=1008M console=ttyS0,115200 root=/dev/mtdblock3 rw rootfstype=jffs2

PID hash table entries: 4096 (order: 2, 16384 bytes)

Dentry cache hash table entries: 131072 (order: 7, 524288 bytes)

Inode-cache hash table entries: 65536 (order: 6, 262144 bytes)

Memory: 1008MB = 1008MB total

Memory: 1015844k/1015844k available, 16348k reserved, 0K highmem

Virtual kernel memory layout:

vector : 0xffff0000 - 0xffff1000 ( 4 kB)

fixmap : 0xfff00000 - 0xfffe0000 ( 896 kB)

vmalloc : 0xbf800000 - 0xff000000 (1016 MB)

lowmem : 0x80000000 - 0xbf000000 (1008 MB)

modules : 0x7f000000 - 0x80000000 ( 16 MB)

.text : 0x80008000 - 0x8065a930 (6475 kB)

.init : 0x8065b000 - 0x806adbc0 ( 331 kB)

.data : 0x806ae000 - 0x806e9990 ( 239 kB)

.bss : 0x806e9990 - 0x80729384 ( 255 kB)

SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1

Hierarchical RCU implementation.

NR_IRQS:16 nr_irqs:16 16

sched_clock: 32 bits at 100MHz, resolution 10ns, wraps every 42949ms

Console: colour dummy device 80x30

Calibrating delay loop... 1196.85 BogoMIPS (lpj=5984256)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 512

CPU: Testing write buffer coherency: ok

ftrace: allocating 17687 entries in 52 pages

CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

Setting up static identity map for 0x804ab220 - 0x804ab278

CPU1: failed to come online

Brought up 1 CPUs

SMP: Total of 1 processors activated (1196.85 BogoMIPS).

CPU: All CPU(s) started in SVC mode.

devtmpfs: initialized

NET: Registered protocol family 16

fpga bridge driver

DMA: preallocated 256 KiB pool for atomic coherent allocations

L310 cache controller enabled

l2x0: 8 ways, CACHE_ID 0x410030c9, AUX_CTRL 0x32460000, Cache size: 524288 B

syscon fffef000.l2-cache: regmap [mem 0xfffef000-0xfffeffff] registered

syscon ffd05000.rstmgr: regmap [mem 0xffd05000-0xffd05fff] registered

syscon ffc25000.sdrctl: regmap [mem 0xffc25000-0xffc25fff] registered

syscon ff800000.l3regs: regmap [mem 0xff800000-0xff800fff] registered

syscon ffd08000.sysmgr: regmap [mem 0xffd08000-0xffd0bfff] registered

hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers.

hw-breakpoint: maximum watchpoint size is 4 bytes.

altera_hps2fpga_bridge fpgabridge.2: fpga bridge [hps2fpga] registered as device hps2fpga

altera_hps2fpga_bridge fpgabridge.2: init-val not specified

altera_hps2fpga_bridge fpgabridge.3: fpga bridge [lshps2fpga] registered as device lwhps2fpga

altera_hps2fpga_bridge fpgabridge.3: init-val not specified

altera_hps2fpga_bridge fpgabridge.4: fpga bridge [fpga2hps] registered as device fpga2hps

altera_hps2fpga_bridge fpgabridge.4: init-val not specified

bio: create slab <bio-0> at 0

FPGA Mangager framework driver

SCSI subsystem initialized

usbcore: registered new interface driver usbfs

usbcore: registered new interface driver hub

usbcore: registered new device driver usb

pps_core: LinuxPPS API ver. 1 registered

pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

PTP clock support registered

Switching to clocksource timer0

NET: Registered protocol family 2

TCP established hash table entries: 8192 (order: 4, 65536 bytes)

TCP bind hash table entries: 8192 (order: 4, 65536 bytes)

TCP: Hash tables configured (established 8192 bind 8192)

TCP: reno registered

UDP hash table entries: 512 (order: 2, 16384 bytes)

UDP-Lite hash table entries: 512 (order: 2, 16384 bytes)

NET: Registered protocol family 1

RPC: Registered named UNIX socket transport module.

RPC: Registered udp transport module.

RPC: Registered tcp transport module.

RPC: Registered tcp NFSv4.1 backchannel transport module.

hw perfevents: enabled with ARMv7 Cortex-A9 PMU driver, 7 counters available

arm-pmu arm-pmu: PMU:CTI successfully enabled for 1 cores

NFS: Registering the id_resolver key type

Key type id_resolver registered

Key type id_legacy registered

NTFS driver 2.1.30 [Flags: R/W].

jffs2: version 2.2. (NAND) © 2001-2006 Red Hat, Inc.

msgmni has been set to 1984

io scheduler noop registered (default)

Serial: 8250/16550 driver, 2 ports, IRQ sharing disabled

ffc02000.serial0: ttyS0 at MMIO 0xffc02000 (irq = 194) is a 16550A

console [ttyS0] enabled

altera_fpga_manager ff706000.fpgamgr: fpga manager [Altera FPGA Manager] registered as minor 0

brd: module loaded

denali-nand-dt ff900000.nand: Dump timing register values:acc_clks: 4, re_2_we: 20, re_2_re: 20

we_2_re: 12, addr_2_data: 14, rdwr_en_lo_cnt: 2

rdwr_en_hi_cnt: 2, cs_setup_cnt: 2

ONFI param page 0 valid

ONFI flash detected

NAND device: Manufacturer ID: 0x2c, Chip ID: 0xda (Micron MT29F2G08ABAEAWP), 256MiB, page size: 2048, OOB size: 64

Bad block table found at page 131008, version 0x01

Bad block table found at page 130944, version 0x01

5 ofpart partitions found on MTD device denali-nand

Creating 5 MTD partitions on "denali-nand":

0x000000000000-0x000001000000 : "NAND Flash Boot Area 16MB"

0x000001000000-0x000002000000 : "NAND Flash Boot Area backup1 16MB"

0x000002000000-0x000003000000 : "NAND Flash Boot Area backup2 16MB"

0x000003000000-0x00000b000000 : "NAND Flash jffs2 Root Filesystem 128MB"

0x00000b000000-0x000010000000 : "NAND Flash jffs2 Root Filesystem 80MB"

dw_spi_mmio fff00000.spi: master is unqueued, this is deprecated

CAN device driver interface

c_can_platform ffc00000.d_can: invalid resource

c_can_platform ffc00000.d_can: control memory is not used for raminit

c_can_platform ffc00000.d_can: c_can_platform device registered (regs=bf8dc000, irq=163)

stmmac_hw_init: 1000M

stmmac - user ID: 0x10, Synopsys ID: 0x37

Ring mode enabled

DMA HW capability register supported

Enhanced/Alternate descriptors

Enabled extended descriptors

RX Checksum Offload Engine supported (type 2)

TX Checksum insertion supported

Enable RX Mitigation via HW Watchdog Timer

libphy: stmmac: probed

eth0: PHY ID 0007c0f1 at 0 IRQ POLL (stmmac-0:00) active

usbcore: registered new interface driver usb-storage

mousedev: PS/2 mouse device common for all mice

i2c /dev entries driver

Synopsys Designware Multimedia Card Interface Driver

dwmmc_socfpga ff704000.dwmmc0: couldn't determine pwr-en, assuming pwr-en = 0

dwmmc_socfpga ff704000.dwmmc0: Using internal DMA controller.

dwmmc_socfpga ff704000.dwmmc0: Version ID is 240a

dwmmc_socfpga ff704000.dwmmc0: DW MMC controller at irq 171, 32 bit host data width, 1024 deep fifo

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 400000Hz, actual 396825HZ div = 63)

dwmmc_socfpga ff704000.dwmmc0: 1 slots initialized

ledtrig-cpu: registered to indicate activity on CPUs

usbcore: registered new interface driver usbhid

usbhid: USB HID core driver

oprofile: using arm/armv7-ca9

TCP: cubic registered

NET: Registered protocol family 10

sit: IPv6 over IPv4 tunneling driver

NET: Registered protocol family 17

NET: Registered protocol family 15

can: controller area network core (rev 20120528 abi 9)

NET: Registered protocol family 29

can: raw protocol (rev 20120528)

can: broadcast manager protocol (rev 20120528 t)

can: netlink gateway (rev 20130117) max_hops=1

8021q: 802.1Q VLAN Support v1.8

Key type dns_resolver registered

VFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4

ThumbEE CPU extension supported.

Registering SWP/SWPB emulation handler

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 300000Hz, actual 297619HZ div = 84)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 200000Hz, actual 200000HZ div = 125)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 100000Hz, actual 100000HZ div = 250)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 400000Hz, actual 396825HZ div = 63)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 300000Hz, actual 297619HZ div = 84)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 200000Hz, actual 200000HZ div = 125)

mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 100000Hz, actual 100000HZ div = 250)

jffs2: Empty flash at 0x01379264 ends at 0x01379800

jffs2: jffs2_scan_inode_node(): CRC failed on node at 0x026f5ff4: Read 0xffffffff, calculated 0x1490a44b

jffs2: Empty flash at 0x026f604c ends at 0x026f6800

jffs2: jffs2_scan_inode_node(): CRC failed on node at 0x053257d0: Read 0xffffffff, calculated 0x89a57f3a

jffs2: Empty flash at 0x05325828 ends at 0x05326000

jffs2: Empty flash at 0x06d4a440 ends at 0x06d4a800

jffs2: Empty flash at 0x071cc00c ends at 0x071cc800

jffs2: jffs2_scan_inode_node(): CRC failed on node at 0x072d0fc8: Read 0xffffffff, calculated 0x05c6c1f6

VFS: Mounted root (jffs2 filesystem) on device 31:3.

devtmpfs: mounted

Freeing unused kernel memory: 328K (8065b000 - 806ad000)

eth0: device MAC address 6e:1f:aa:4f:59:2e

init phy ok

PHY DMA init OK

eth0: device MAC address 00:87:9f:01:9a:3e

init phy ok

PHY DMA init OK

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

libphy: stmmac-0:00 - Link is Up - 100/Full

IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

libphy: stmmac-0:00 - Link is Down

In axi fpga driver!

Original value in RESET_MANAGER_BASE_ADDR + BRGMODRST_ADDR is 0x0

request_mem_region OK!

AXI fpga dev virtual address is 0xbf942000

*base_vir_addr = 0xc50f

In fpga mem driver!

request_mem_region OK!

fpga mem virtual address is 0xc0000000

libphy: stmmac-0:00 - Link is Up - 100/Full

eth0: device MAC address 00:87:9f:01:9a:3e

init phy ok

PHY DMA init OK

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

eth0: device MAC address 00:87:9f:01:9a:3e

init phy ok

PHY DMA init OK

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

libphy: stmmac-0:00 - Link is Up - 100/Full

IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

libphy: stmmac-0:00 - Link is Down

libphy: stmmac-0:00 - Link is Up - 100/Full

This is C5 board.

DETECT HW version=0000c50f

Miner Type = R4

AsicType = 1387

real AsicNum = 63

get PLUG ON=0x00000005

Find hashboard on Chain[0]

Find hashboard on Chain[2]

set_reset_allhashboard = 0x0000ffff

Check chain[0] PIC fw version=0x03

Check chain[2] PIC fw version=0x03

chain[0] has no freq in PIC! Will use default freq=550 and jump over...

Check chain[0] PIC fw version=0x03

chain[2] has no freq in PIC! Will use default freq=550 and jump over...

Check chain[2] PIC fw version=0x03

get PIC voltage=91 on chain[0], value=890

get PIC voltage=91 on chain[2], value=890

set_reset_allhashboard = 0x00000000

chain[0] temp offset record: 3,-71,4,-88,0,0,0,0

chain[2] temp offset record: 3,-81,4,-108,0,0,0,0

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

CRC error counter=0

set command mode to VIL

--- check asic number

set_baud=0

The min freq=700

set real timeout 52, need sleep=379392

After TEST CRC error counter=0

search freq for 1 times, completed chain = 2, total chain num = 2

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

restart Miner chance num=2

waiting for receive_func to exit!

waiting for pic heart to exit!

Start bmminer ...

This is C5 board.

Miner Type = R4

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x0000ffff

Check chain[0] PIC fw version=0x03

Check chain[2] PIC fw version=0x03

Chain[J1] orignal chain_voltage_pic=91 value=890

Chain[J3] orignal chain_voltage_pic=91 value=890

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

Chain[J1] has 63 asic

Chain[J3] has 63 asic

Chain[J1] has no freq in PIC, set default freq=550M

Chain[J1] has no core num in PIC

Chain[J3] has no freq in PIC, set default freq=550M

Chain[J3] has no core num in PIC

read PIC voltage=940 on chain[0]

Chain:0 chipnum=63

Chain[J1] voltage added=0.0V

Chain:0 temp offset=0

Chain:0 base freq=550

Asic[ 0]:550

Asic[ 1]:550 Asic[ 2]:550 Asic[ 3]:550 Asic[ 4]:550 Asic[ 5]:550 Asic[ 6]:550 Asic[ 7]:550 Asic[ 8]:550

Asic[ 9]:550 Asic[10]:550 Asic[11]:550 Asic[12]:550 Asic[13]:550 Asic[14]:550 Asic[15]:550 Asic[16]:550

Asic[17]:550 Asic[18]:550 Asic[19]:550 Asic[20]:550 Asic[21]:550 Asic[22]:550 Asic[23]:550 Asic[24]:550

Asic[25]:550 Asic[26]:550 Asic[27]:550 Asic[28]:550 Asic[29]:550 Asic[30]:550 Asic[31]:550 Asic[32]:550

Asic[33]:550 Asic[34]:550 Asic[35]:550 Asic[36]:550 Asic[37]:550 Asic[38]:550 Asic[39]:550 Asic[40]:550

Asic[41]:550 Asic[42]:550 Asic[43]:550 Asic[44]:550 Asic[45]:550 Asic[46]:550 Asic[47]:550 Asic[48]:550

Asic[49]:550 Asic[50]:550 Asic[51]:550 Asic[52]:550 Asic[53]:550 Asic[54]:550 Asic[55]:550 Asic[56]:550

Asic[57]:550 Asic[58]:550 Asic[59]:550 Asic[60]:550 Asic[61]:550 Asic[62]:550

Chain:0 max freq=550

Chain:0 min freq=550 which is far less annoying... |

|

|

|

zachj00

Jr. Member

Offline Offline

Activity: 120

Merit: 2

|

|

January 18, 2019, 10:33:37 PM |

|

Sorry  Still learning. Ill edit it rn! |

|

|

|

|

Artemis3

Legendary

Offline Offline

Activity: 2016

Merit: 1563

CLEAN non GPL infringing code made in Rust lang

|

|

January 18, 2019, 10:40:35 PM |

|

Is it possible you're one of the few with an incompatible control board? Can you post the start up sequence from the kernel log? Curious if you have neither 512 or 1024 mb like mentioned in the FW title.

Also, check and see if your control board says XILINX on it. If not, the AB FW is incompatible with your board.

Heres the first part of the kernal log. Machine: Altera SOCFPGA, model: Altera SOCFPGA Cyclone V

...

Memory: 1008MB = 1008MB total Mine is: Machine model: Xilinx Zynq

...

Memory: 884148K/1032192K available We both have 1024 mb of ram... |

█████████████████████████

██████████████████████████

██████████████████████████

███████████████████████████ | BRAIINS OS+| | AUTOTUNING

MINING FIRMWARE| | Increase hashrate on your Bitcoin ASICs,

improve efficiency as much as 25%, and

get 0% pool fees on Braiins Pool | |

|

|

|

sarcheer

Copper Member

Full Member

Offline Offline

Activity: 330

Merit: 103

|

|

January 18, 2019, 11:33:47 PM |

|

Heres the first part of the kernal log. Machine: Altera SOCFPGA, model: Altera SOCFPGA Cyclone V

...

Memory: 1008MB = 1008MB total Mine is: Machine model: Xilinx Zynq

...

Memory: 884148K/1032192K available We both have 1024 mb of ram... Well that explains why the AB firmware wont install for zachj00, its only compatible with the Xilinx boards. I wasnt sure if he could get the 2017-04-28 FW, so was checking to see if his board didnt have the requisite 512 or 1024 mb of ram. Zach, can you tell us exactly what your R4 overview page says for your File System Version? Im curious if youre on a different 2017 FW that BM no longer allows us to download. |

Miners:

Avalon 1041, Whatsminer M10, Antminer T15 x 2, DragonMint T1 x 3, Innosilicon T2T, R4 x 2

|

|

|

sarcheer

Copper Member

Full Member

Offline Offline

Activity: 330

Merit: 103

|

|

January 18, 2019, 11:41:15 PM |

|

I see in the description and the manual for the APW5 that there is supposed to be an ability for the user to change output lines and fine-tune the output voltage. Any ideas on how to adjust the output voltage? Heres what the inside of one of my APW5s looks like:  |

Miners:

Avalon 1041, Whatsminer M10, Antminer T15 x 2, DragonMint T1 x 3, Innosilicon T2T, R4 x 2

|

|

|

philipma1957

Legendary

Offline Offline

Activity: 4102

Merit: 7723

'The right to privacy matters'

|

|

January 18, 2019, 11:58:58 PM |

|

I see in the description and the manual for the APW5 that there is supposed to be an ability for the user to change output lines and fine-tune the output voltage. Any ideas on how to adjust the output voltage? Heres what the inside of one of my APW5s looks like:  sure there is a term pot on the upper right side. but I think you will not get it to go to 18 volts maybe to 16 also protect the negative and positive cables they are a short danger |

|

|

|

sarcheer

Copper Member

Full Member

Offline Offline

Activity: 330

Merit: 103

|

|

January 19, 2019, 12:24:21 AM |

|

I see in the description and the manual for the APW5 that there is supposed to be an ability for the user to change output lines and fine-tune the output voltage. Any ideas on how to adjust the output voltage? Heres what the inside of one of my APW5s looks like: https://i.imgur.com/OiRz1qH.pngsure there is a term pot on the upper right side. but I think you will not get it to go to 18 volts maybe to 16 also protect the negative and positive cables they are a short danger Is that pot something I can adjust while the PSU is powered? |

Miners:

Avalon 1041, Whatsminer M10, Antminer T15 x 2, DragonMint T1 x 3, Innosilicon T2T, R4 x 2

|

|

|

philipma1957

Legendary

Offline Offline

Activity: 4102

Merit: 7723

'The right to privacy matters'

|

|

January 19, 2019, 02:28:46 AM |

|

I see in the description and the manual for the APW5 that there is supposed to be an ability for the user to change output lines and fine-tune the output voltage. Any ideas on how to adjust the output voltage? Heres what the inside of one of my APW5s looks like: https://i.imgur.com/OiRz1qH.pngsure there is a term pot on the upper right side. but I think you will not get it to go to 18 volts maybe to 16 also protect the negative and positive cables they are a short danger Is that pot something I can adjust while the PSU is powered? I would be very careful doing it powered up. That unit has lots of power in it. It has short a short hazard in the six power points. You could mod it drill a hole with access to the pot and mount a nylon sleeve https://www.amazon.com/Electronics-Salon-Spacer-Assortment-Screws-Plastic/dp/B014KISXAG/ref=sr_1_2_sspa?then the screwdriver can not hit anything but the pot. |

|

|

|

zachj00

Jr. Member

Offline Offline

Activity: 120

Merit: 2

|

|

January 21, 2019, 10:37:21 PM |

|

Heres the first part of the kernal log. Machine: Altera SOCFPGA, model: Altera SOCFPGA Cyclone V

...

Memory: 1008MB = 1008MB total Mine is: Machine model: Xilinx Zynq

...

Memory: 884148K/1032192K available We both have 1024 mb of ram... Well that explains why the AB firmware wont install for zachj00, its only compatible with the Xilinx boards. I wasnt sure if he could get the 2017-04-28 FW, so was checking to see if his board didnt have the requisite 512 or 1024 mb of ram. Zach, can you tell us exactly what your R4 overview page says for your File System Version? Im curious if youre on a different 2017 FW that BM no longer allows us to download. Miner Type Antminer R4 Hostname antMiner Model GNU/Linux Hardware Version 15.0.1.3 Kernel Version Linux 3.10.31-ltsi-00003-gcf03eb9 #81 SMP Mon Apr 25 11:20:36 CST 2016 File System Version Sat Apr 29 20:06:46 EDT 2017 BMminer Version 2.0.0 Uptime 1 Load Average 0.80, 0.69, 0.66 Memory Total Available 54724 kB / 1016172 kB (5%) Free 961448 kB / 1016172 kB (95%) Cached 0 kB / 1016172 kB (0%) Buffered 0 kB / 1016172 kB (0%) |

|

|

|

|

Artemis3

Legendary

Offline Offline

Activity: 2016

Merit: 1563

CLEAN non GPL infringing code made in Rust lang

|

|

January 21, 2019, 11:10:18 PM Merited by vapourminer (2) |

|

Heres the first part of the kernal log. Machine: Altera SOCFPGA, model: Altera SOCFPGA Cyclone V

...

Memory: 1008MB = 1008MB total Mine is: Machine model: Xilinx Zynq

...

Memory: 884148K/1032192K available We both have 1024 mb of ram... Well that explains why the AB firmware wont install for zachj00, its only compatible with the Xilinx boards. I wasnt sure if he could get the 2017-04-28 FW, so was checking to see if his board didnt have the requisite 512 or 1024 mb of ram. Zach, can you tell us exactly what your R4 overview page says for your File System Version? Im curious if youre on a different 2017 FW that BM no longer allows us to download. Miner Type Antminer R4 Hostname antMiner Model GNU/Linux Hardware Version 15.0.1.3 Kernel Version Linux 3.10.31-ltsi-00003-gcf03eb9 #81 SMP Mon Apr 25 11:20:36 CST 2016 File System Version Sat Apr 29 20:06:46 EDT 2017 Bitmain is showing both Antminer-R4-all-201704270142-autofreq-user-Update2UBI-NF.tar.gz and Antminer-R4-all-201704280718-autofreq-user-Update2UBI-NF.tar.gz, but the date for "file system version" seems close enough... I wonder why Bitmain chose to leave both online if April 28 fixes "a bug of memory leak" from April 27? BTW: My Hardware Version is 30.0.1.3 |

█████████████████████████

██████████████████████████

██████████████████████████

███████████████████████████ | BRAIINS OS+| | AUTOTUNING

MINING FIRMWARE| | Increase hashrate on your Bitcoin ASICs,

improve efficiency as much as 25%, and

get 0% pool fees on Braiins Pool | |

|

|

|

fishdogduck

Newbie

Offline Offline

Activity: 22

Merit: 3

|

Hello, Just seeing if anyone is still runnings their R4 and should I update anything or just keep things the way they are seen as it is still working? Would be nice if I could increase the efficiency even if it means a lower hashrate. https://i.imgur.com/dABpVmJ.pngMiner Type Antminer R4 Hostname antMiner Model GNU/Linux Hardware Version 30.0.1.3 Kernel Version Linux 3.14.0-xilinx-gb190cb0-dirty #57 SMP PREEMPT Fri Dec 9 14:49:22 CST 2016 File System Version Sat Apr 29 20:06:48 EDT 2017 BMminer Version 2.0.0 |

|

|

|

|

slurfius

Jr. Member

Offline Offline

Activity: 100

Merit: 6

|

|

May 09, 2022, 12:16:44 AM |

|

Braiins OS+ does amazing things for an s9. The s9 controller is the same as an R4. So I installed the braiins os+ and it does a good job improving efficiency for r4 too.

|

|

|

|

|

fishdogduck

Newbie

Offline Offline

Activity: 22

Merit: 3

|

|

May 11, 2022, 08:34:15 AM |

|

Braiins OS+ does amazing things for an s9. The s9 controller is the same as an R4. So I installed the braiins os+ and it does a good job improving efficiency for r4 too.

Awesome thanks, I'll check it out. Is it fairy simple to install? I have pretty much zero knowlege of ASIC miners after coming from GPU mining. |

|

|

|

|

slurfius

Jr. Member

Offline Offline

Activity: 100

Merit: 6

|

|

May 13, 2022, 12:53:49 AM |

|

I used the run from sd card install method on all my antminers. Besides moving the jumper on the control board (which is a pain in the ass to reach on the s9) it is very easy and you can revert right back just by moving the jumper back and removing the sd card. Link to download the s9 firmware https://braiins.com/os/plus/download |

|

|

|

|

|