|

scrybe

|

|

October 22, 2012, 04:01:27 AM |

|

I wonder what the ARM place holder is for ? how could an ARM chip benefit the board ?

Add a network jack and some ram and you'd be able to have a low power standalone miner --- maybe? That would work if the board had place holders for those additional things, but it does not so it would need a board re-design, which makes it pointless placing an ARM holder on the current board. what are the chances they could rework the bitstream on the Altera to drive an Ethernet or WiFi shield attached to one or both of those minirig-sc ports? It does seem interesting to have that ARM label there in what seems to be a very logically thought out board otherwise. |

"...as simple as possible, but no simpler" -AE

BTC/TRC/FRC: 1ScrybeSNcjqgpPeYNgvdxANArqoC6i5u Ripple:rf9gutfmGB8CH39W2PCeRbLWMKRauYyVfx LTC:LadmiD6tXq7gFZvMibhFUZegUHKXgbu1Gb

|

|

|

|

|

|

|

|

If you see garbage posts (off-topic, trolling, spam, no point, etc.), use the "report to moderator" links. All reports are investigated, though you will rarely be contacted about your reports.

|

|

|

Advertised sites are not endorsed by the Bitcoin Forum. They may be unsafe, untrustworthy, or illegal in your jurisdiction.

|

|

|

|

|

|

|

|

Enigma81

|

|

October 22, 2012, 09:28:11 AM |

|

I wonder what the ARM place holder is for ? how could an ARM chip benefit the board ?

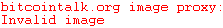

Add a network jack and some ram and you'd be able to have a low power standalone miner --- maybe? That would work if the board had place holders for those additional things, but it does not so it would need a board re-design, which makes it pointless placing an ARM holder on the current board. Has anyone seen the back side of the board? High speed DDR is often soldered right behind the processor.. And..  Something like this...  |

|

|

|

|

|

bce

|

|

October 22, 2012, 09:52:46 AM |

|

Updated wallpaper   |

|

|

|

|

|

Xfinity

|

|

October 22, 2012, 12:49:47 PM |

|

Wallpaper

Nice one  . On topic: I like the formfactor very much on these PCBs. Easy to cool. |

Donations (BTC): 1L8EcGAuaDNK4kNxAbEBawo8ZaeFZvibgj

|

|

|

Epoch

Legendary

Offline Offline

Activity: 922

Merit: 1003

|

|

October 22, 2012, 02:50:54 PM

Last edit: October 22, 2012, 03:24:59 PM by Epoch |

|

On topic: I like the formfactor very much on these PCBs. Easy to cool.

It is the same form factor as the current FPGA Singles. The ASICs themselves appear to have a plastic top; not the most efficient thermal interface to a top-mounted metal heatsink. Although 7W/chip isn't huge, the combination of 8 of them in close proximity generates a lot of concentrated heat. Transferring 60W from plastic chips to a metal heatsink can be a challenge. Also, mounting a monolithic heatsink across 8 separate chips poses another challenge: if those chips are not coplanar, the contact between the heatsink and some of the chips will not be 'perfect'; the gap will be taken up by the thermal transfer compound which would further restrict thermal conductivity. The good news is that the SC Single uses less power than the FPGA Single, which will mitigate the situation a bit. Plus, the 8 ASIC chips, though plastic, have an overall larger surface area then the 2 metal-top FPGAs in the old Singles. More surface area makes it easier to transfer heat. So all in all I don't think cooling these will be an issue; I'm sure BFL has already thought of all this and they have plenty of experience with the FPGA Singles. The SC board is 92mmx92mm, so it seems clear from the mounting holes that BFL will continue to use a standard 92mm fan for cooling. |

|

|

|

|

Inaba

Legendary

Offline Offline

Activity: 1260

Merit: 1000

|

|

October 22, 2012, 03:12:29 PM |

|

The pics with Henrietta are taken with my 5DMk2, though I scale them down for the web of course.

We actually agonized a lot over the plastic issue and went through scenario after scenario due to specifically that fact. There a bunch of vias on the bottom of the board, and we were originally going to cool it from the bottom instead of the top, but simulation after simulation showed it was more effective from the top, so that's what we went with. But the vias are still there for a bit of extra oomph when the clock rate is bumped up.

There's a pic of the back of the board on the BFL forums.

|

If you're searching these lines for a point, you've probably missed it. There was never anything there in the first place.

|

|

|

crazyates

Legendary

Offline Offline

Activity: 952

Merit: 1000

|

|

October 22, 2012, 03:33:16 PM |

|

On topic: I like the formfactor very much on these PCBs. Easy to cool.

It is the same form factor as the current FPGA Singles. The ASICs themselves appear to have a plastic top; not the most efficient thermal interface to a top-mounted metal heatsink. Although 7W/chip isn't huge, the combination of 8 of them in close proximity generates a lot of concentrated heat. Transferring 60W from plastic chips to a metal heatsink can be a challenge. Also, mounting a monolithic heatsink across 8 separate chips poses another challenge: if those chips are not coplanar, the contact between the heatsink and some of the chips will not be 'perfect'; the gap will be taken up by the thermal transfer compound which would further restrict thermal conductivity. The good news is that the SC Single uses less power than the FPGA Single, which will mitigate the situation a bit. Plus, the 8 ASIC chips, though plastic, have an overall larger surface area then the 2 metal-top FPGAs in the old Singles. More surface area makes it easier to transfer heat. So all in all I don't think cooling these will be an issue; I'm sure BFL has already thought of all this and they have plenty of experience with the FPGA Singles. The SC board is 92mmx92mm, so it seems clear from the mounting holes that BFL will continue to use a standard 92mm fan for cooling. This is the very reason why most RAM chips you see use Termal Pads, rathern than a compound. Any possibility that pads would be used instead of compound, or would 60W be too much for them? |

|

|

|

Epoch

Legendary

Offline Offline

Activity: 922

Merit: 1003

|

|

October 22, 2012, 03:35:36 PM |

|

We actually agonized a lot over the plastic issue and went through scenario after scenario due to specifically that fact. There a bunch of vias on the bottom of the board, and we were originally going to cool it from the bottom instead of the top, but simulation after simulation showed it was more effective from the top, so that's what we went with. But the vias are still there for a bit of extra oomph when the clock rate is bumped up.

It may be worthwhile putting a passive heatsink on the bottom as well to give the device more thermal headroom. Some/most/all of my FPGA Singles have this (some also have a small fan at the bottom). I do hope it does not become necessary to put a small fan at the bottom of the board; the FPGA Singles that have it can be very/too loud and makes it impossible to create a 'quiet Single' by replacing the top main fan only. And since the ASICs will likely not be 'under-clockable', we would be limited in how far we can reduce airflow to reduce noise (the FPGA Singles can be loaded with slower firmware to reduce thermal output; not so with ASICs unfortunately). I suspect we won't really know the answer to this until BFL has had a chance to run these things at full load in an actual enclosure. |

|

|

|

|

|

RHA

|

|

October 22, 2012, 04:39:02 PM |

|

There's a pic of the back of the board on the BFL forums.

It's not always easy to find something there, so the link is: the back of the board |

|

|

|

|

squid

Member

Offline Offline

Activity: 112

Merit: 10

|

|

October 22, 2012, 04:40:54 PM |

|

There's a pic of the back of the board on the BFL forums.

It's not always easy to find something there, so the link is: the back of the boardHave to login to view =[ |

|

|

|

|

|

Xfinity

|

|

October 22, 2012, 05:04:56 PM

Last edit: October 22, 2012, 07:15:46 PM by Xfinity |

|

It may be worthwhile putting a passive heatsink on the bottom as well to give the device more thermal headroom. Some/most/all of my FPGA Singles have this (some also have a small fan at the bottom).

What passive heatsink are you using on the bottom? |

Donations (BTC): 1L8EcGAuaDNK4kNxAbEBawo8ZaeFZvibgj

|

|

|

crazyates

Legendary

Offline Offline

Activity: 952

Merit: 1000

|

|

October 22, 2012, 05:15:34 PM |

|

It may be worthwhile putting a passive heatsink on the bottom as well to give the device more thermal headroom. Some/most/all of my FPGA Singles have this (some also have a small fan at the bottom).

What passive heatsink are you using on the bottom?    |

|

|

|

Epoch

Legendary

Offline Offline

Activity: 922

Merit: 1003

|

|

October 22, 2012, 06:03:57 PM |

|

It may be worthwhile putting a passive heatsink on the bottom as well to give the device more thermal headroom. Some/most/all of my FPGA Singles have this (some also have a small fan at the bottom).

What passive heatsink are you using on the bottom? Many of the shipping FPGA Singles have a passive heatsink on the bottom already. I was just suggesting that a similar approach could be taken (by BFL) for the SC Singles. |

|

|

|

|

|

bce

|

|

October 22, 2012, 07:53:56 PM |

|

If the boards are already made, and asics already placed, something like this would probably be enough:  What'd be ideal is if these were almost exactly the same height as the space between bottom of board to enclosure, so that if the thermal adhesive proves not to be reliable, at least the heatsinks will be kept in place (not a bunch of copper pieces shaking around and contacting the board). Would it be possible to solder something like this to the board before the ASIC chips are placed? |

|

|

|

|

|

psilan

|

|

October 22, 2012, 08:08:57 PM |

|

Here we go. |

dip

|

|

|

|

|

|

dooferorg

|

|

October 22, 2012, 08:43:13 PM |

|

Pictures with the pig with wings to indicate that we'll get them ... when pigs fly?  |

BTC: 1dooferoD3vnwgez3Jo1E4bFfgMf81LR2

ZEC: t1gnToN2HZW4GD52kofEVdijhRijWjCNfYi

|

|

|

|

abeaulieu

|

|

October 22, 2012, 08:44:38 PM |

|

The pics with Henrietta are taken with my 5DMk2, though I scale them down for the web of course.

We actually agonized a lot over the plastic issue and went through scenario after scenario due to specifically that fact. There a bunch of vias on the bottom of the board, and we were originally going to cool it from the bottom instead of the top, but simulation after simulation showed it was more effective from the top, so that's what we went with. But the vias are still there for a bit of extra oomph when the clock rate is bumped up.

There's a pic of the back of the board on the BFL forums.

I actually find this hard to believe since the footprint of your ASIC looks to have a pad on the bottom for grounding and thermal dissipation (often called a heat slug). Usually the thermal conductivity to this pad is much higher than to the plastic case (I think I saw that ngzhang also mentioned this somewhere). Also, if you hadn't tented the vias on the bottom you'd get a higher thermal conduction to your heatsink (soldermask tends to be a thermal insulator). Is this a 6 layer pcb? |

|

|

|

|

|

abeaulieu

|

|

October 22, 2012, 08:49:51 PM |

|

I wonder what the ARM place holder is for ? how could an ARM chip benefit the board ?

I'm guessing that they put down that footprint to support a standalone miner eventually. Since there is starting to be plenty of mining software support for ARM processors (I'm mining on my Raspberry Pi currently), it wouldn't take much to run a light version on linux on-board the ARM processor to act as the controller. |

|

|

|

|

|

michaelmclees

|

|

October 22, 2012, 09:59:07 PM |

|

If the boards are already made, and asics already placed, something like this would probably be enough:  What'd be ideal is if these were almost exactly the same height as the space between bottom of board to enclosure, so that if the thermal adhesive proves not to be reliable, at least the heatsinks will be kept in place (not a bunch of copper pieces shaking around and contacting the board). Would it be possible to solder something like this to the board before the ASIC chips are placed? That's what I keep thinking. If the ships are not perfectly level, you're other going to crush them with the heatsink, or you're going to not have good contact with all of them. Why not just use these little guys? |

|

|

|

|

|